Basic Image processing

Crop image

Crop เป็นการแบ่งภาพเฉพาะส่วน หรือก็คือเป็นความสามารถในการแบ่งส่วนอาร์เรย์ของ NumPy

$ image[y_start:y_end, x_start:x_end]โดยที่ image คือ ตัวแปรเก็บภาพที่ต้องการนำมาแสดงภาพเฉพาะส่วน ซึ่งตัวแปรเก็บภาพอาจเป็นชื่ออื่นที่ไม่ใช่ image ก็ได้ เช่น

my_img = cv2.imread("path/your/image.jpg")

crop = my_img[0:100,0:500]ตัวแปร crop จะทำการเก็บภาพเฉพาะตำแหน่ง (0,0) ถึง (100,500)

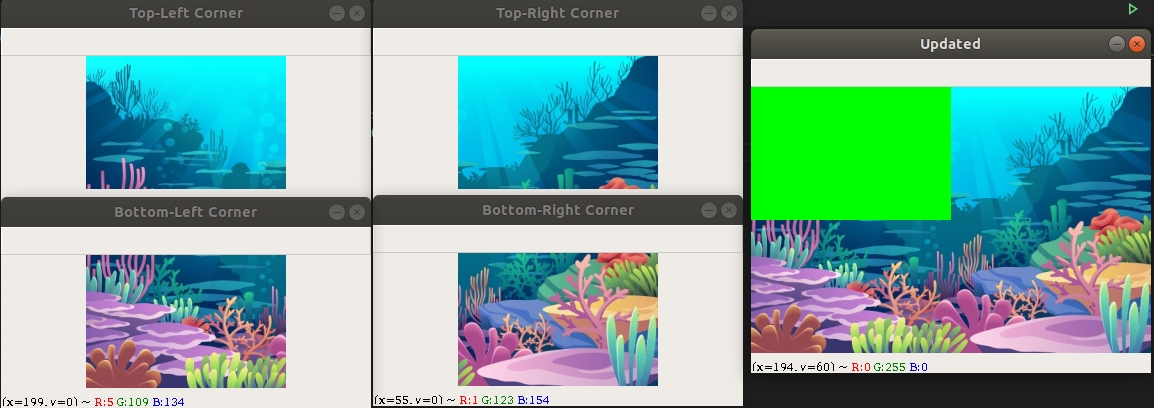

Example:

import cv2

import imutils

image = cv2.imread("path/your/image.jpg")

image = imutils.resize(image,width = 400)

(h, w) = image.shape[:2]

(cX, cY) = (w // 2, h // 2) tl = image[0:cY, 0:cX]cv2.imshow("Top-Left Corner", tl)

tr = image[0:cY, cX:w]

cv2.imshow("Top-Right Corner", tr)

br = image[cY:h, cX:w]

cv2.imshow("Bottom-Right Corner", br)

bl = image[cY:h, 0:cX]

cv2.imshow("Bottom-Left Corner", bl)

image[0:cY, 0:cX] = (0, 255, 0)

cv2.imshow("Updated", image)

cv2.waitKey(0)บรรทัดที่ 8 : หาจุดกึ่งกลางของภาพ

บรรทัดที่ 10, 13, 16, 19 : แบ่งภาพที่ตำแหน่งที่ต้องการ

บรรทัดที่ 22 : กำหนดให้ภาพที่ตำแหน่ง [0:cY, 0:cX] เป็นสีเขียว

Bitwise

Bitwise เป็นตัวดำเนินการทางตรรกศาสตร์ (AND, OR, XOR, NOT) ซึ่งตัวดำเนินการนี้จะใช้กับภาพที่เป็นไบนารี่เท่านั้น

AND

$ cv2.bitwise_and(image1, image2)OR

$ cv2.bitwise_or(image1, image2)XOR

$ cv2.bitwise_xor(image1, image2)NOT

$ cv2.bitwise_not(image)Example:

import numpy as np

import cv2

rectangle = np.zeros((300, 300), dtype = "uint8")

cv2.rectangle(rectangle, (25, 25), (275, 275), 255, -1)

cv2.imshow("Rectangle", rectangle)

circle = np.zeros((300, 300), dtype = "uint8")

cv2.circle(circle, (150, 150), 150, 255, -1)

cv2.imshow("Circle", circle)

bitwiseAnd = cv2.bitwise_and(rectangle, circle)

cv2.imshow("AND", bitwiseAnd)

bitwiseOr = cv2.bitwise_or(rectangle, circle)

cv2.imshow("OR", bitwiseOr)

bitwiseXor = cv2.bitwise_xor(rectangle, circle)

cv2.imshow("XOR", bitwiseXor)

bitwiseNot = cv2.bitwise_not(circle)

cv2.imshow("NOT", bitwiseNot)

cv2.waitKey(0)

Last updated

Was this helpful?